MasPar

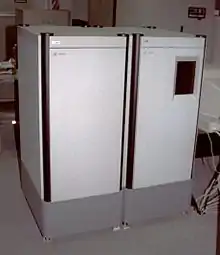

MasPar Computer Corporation — американская компания, производитель минисуперкомпьютеров, основана в 1987 году Джеффом Кэлбом. Компания располагалась в Саннивейле (Калифорния). Штат компании состоял из 100 человек.

История

Пока Кэлб был вице-президентом подразделения по производству интегральных микросхем в DEC, некоторые исследователи из этого подразделения спроектировали суперкомпьютер на основе суперкомпьютера с массовым параллелизмом Goodyear MPP. Исследователи из DEC улучшили архитектуру:

- процессорные элементы стали 4-битными вместо 1-битных

- увеличилось количество возможных соединений каждого процессора с соседними с 4 до 8

- добавилось глобальное взаимодействие всех процессорных элементов, которое было реализовано при помощи коммутатора с тройным резервированием, что проще для реализации, чем полный матричный переключатель.

После того как в DEC решили не выпускать исследовательский проект на рынок, Кэлб создал компанию для продажи разработанного минисуперкомпьютера. В 1990 году было выпущено первое поколение — MP-1. За ним, в 1992 году, последовал MP-2. Всего компания выпустила более 200 компьютеров. Компьютеры MasPar приобретались многими суперкомпьютерными центрами и корпорациями вроде Ford и American Express. Экземпляры систем MasPar из Центра космических полётов Годдарда (NASA) хранятся в Музее компьютерной истории.

MasPar являлась вторым после DEC поставщиком SIMD-машин.

В 1996 году компания прекратила разработку аппаратного обеспечения и преобразовалась в компанию, занимающуюся программным обеспечением для сбора и анализа данных, под названием Neovista Software. В 1999 году Neovista была приобретена компанией Accrue Software, которая в свою очередь стала подразделением компании JDA Software в 2001 году.[1][2]

Аппаратное обеспечение

Компьютеры серий MP-1 и MP-2 относятся к классу SIMD-машин.

Архитектура машин MasPar состоит из 2 основных частей: интерфейсной части и устройства параллельной обработки данных (DPU).

В качестве интерфейсной части выступает стандартная рабочая станция (обычно VAX или DECstation), посредством которой осуществляется доступ пользователей к DPU. Есть возможность подключения высокоскоростных устройств ввода-вывода и прямого доступа к адресной шине DEC.

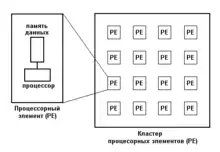

DPU является подсистемой, обеспечивающей массовую параллельную обработку данных и состоит из 2 частей: устройства управления массивом (ACU) и массива процессорных элементов (PE array), производящего параллельные вычисления.

Устройство управления массивом управляет массивом процессорных элементов и обеспечивает доступ к глобальной памяти совместно используемой всеми процессорными элементами. ACU осуществляет широковещательные передачи массивам процессорных элементов инструкций и совместно используемых переменных по шине ACU-PE-Bus, а также производит операции над последовательными данными в параллельной программе, которые хранятся в глобальной памяти. Устройство управления массивом использует для памяти инструкций алгоритм замещения страниц виртуальной памяти по запросу. ACU представляет собой RISC-подобный процессор, созданный на основе стандартных микросхем производства Texas Instruments.

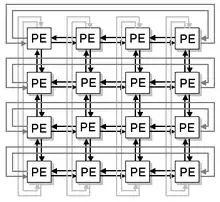

Массив процессорных элементов имеет топологию двухмерной решетки размером до 128 на 128 элементов, противоположные грани которой соединены, образуя тор, что обеспечивает обмен данными между первыми и последними элементами строк и столбцов. Внутри решетки процессоры разделены на кластеры размером 4 на 4 элемента. Каждый процессорный элемент имеет от 16 до 64 Кбайт локальной памяти данных DRAM с высокоскоростным доступом к ней, благодаря чему не нуждается в кеш-памяти. Ширина шины памяти — 16 бит. Поддерживаются как big-endian, так и little-endian форматы. Поддерживается прямая и непрямая (косвенная) адресация памяти данных. Процессорные элементы не осуществляют управления памятью данных. Также каждый процессорный элемент содержит 64 32-битных регистра, которые используются как для целочисленных, так и для вещественночисленных данных. Регистры, что примечательно, с адресацией битов и байтов. Над вещественночисленными данными выполняются арифметические действия одинарной и двойной точности в формате IEEE 754. Каждый процессорный элемент также имеет два битовых последовательных порта, один для входящих и один для исходящих коммуникаций с ближайшими соседями по X-сети. Последовательные соединения поддерживают передачу битовых последовательностей со скоростью 1 Мбайт/с, что позволяет координировать соединения регистр-регистр между процессорами.

Процессорные элементы спроектированы и изготовлены по специальному заказу для MasPar и защищены патентами. Каждый процессорный элемент может делать свою собственную выборку данных, но все они управляются устройством управления массивом (ACU). Процессорные элементы имеют RISC-архитектуру и представляет собой двухуровневую интегральную КМОП-микросхему, изготовленную по 1,0 мкм технологическому процессу, с рассеиваемой мощностью 0,8 Вт и упакованную в 208-контактный PQFP-корпус. Тактовая частота — 12,5 МГц.

Обмен данными между процессорами может выполняться двумя способами:

- Для регулярного обмена данными каждый из процессорных элементов соединен со своими ближайшими 8-ю соседями, образуя так называемую X-сеть (X-Net). В любой момент передача данных по X-сети возможна только в одном из 8 направлений, при этом каждый процессорный элемент может посылать данные через соединение с соответствующей стороны и получать данные с противоположной. Если расстояние между взаимодействующими процессорными элементами больше 1, то данные пересылаются с промежуточным хранением. Стоимость перемещения данных пропорциональна расстоянию.

- Другой коммуникационный механизм предоставляется глобальным маршрутизатором (Global router, GR), допускающим произвольные межпроцессорные соединения. Маршрутизатор используется там, где нельзя предсказать перемещение данных, где требуются пересылки на дальнее расстояние. Тем не менее следует помнить, что время установки соединения через глобальный маршрутизатор значительно превосходит его же в X-net и, что существует только одно входное и одно выходное соединение для каждого кластера процессорных элементов. Соответственно, коммуникационные операции выполняются последовательно всегда, когда требуется более одного входящего или одного исходящего соединения на кластер.

Скорость передачи данных составляет 18 Гбайт/с при обмене между ближайшими соседями в машине с 16 384 процессорными элементами и 1300 Мбайт/с при передаче данных через глобальный маршрутизатор.

Система может содержать от 1024 до 16 384 процессорных элементов. Производительность машины с 16 384 процессорными элементами составляет 1,2 GFLOPS (2,6 GIPS). Заявленное производителем среднее время наработки на отказ составляет более 8000 часов. Специальных возможностей для отказоустойчивой работы не предусмотрено. При стоимости машины с 16 384 процессорами в 500 000 фунтов цена 1 GFLOPS составляет 450 000 фунтов. Машина позиционируется на рынке как высоконадёжный компьютер для самых ресурсоёмких применений. Парк установленных машин достаточно мал. Типичными приложениями выполняемыми на MP-1 являются подбор ДНК-последовательностей и устранение размытости изображений.

В серии MP-1 и MP-2 входили по 5 моделей, различающихся количеством процессорных элементов, объёмом локальной памяти каждого процессорного элемента и скоростью обмена данными между процессорными элементами.

- Серия MP-1 включала модели: MP1101, MP1102, MP1104, MP1208, MP1216.

- Серия MP-2 включала модели: MP2201, MP2202, MP2204, MP2208, MP2216.

Программное обеспечение

Компьютеры MasPar работали с операционной системой UNIX, компиляторами Си и Фортрана, обладали развитым графическим программным окружением и прочими инструментами.

Из языков программирования поддерживаются ANSI-совместимый Си и MasPar Fortran (MPF), который является переработанной в компании версией Fortran 90. Программное окружение MasPar Program Environment (MPPE) является лицензированной версией транслятора Фортрана VAST-2 компании Pacific-Sierra Research Corporation. Этот продукт преобразует последовательный исходный код на Fortran 77 в распараллеленный исходный код на MPF. Также может быть совершено обратное преобразование.

Примечания

- Bloomberg Businessweek, Company Overview of Neovista Software, Inc.

- DSstar Vol. 5 No. 27 (July 3, 2001), JDA Software Buys Accrue Software's NeoVista DM Products Архивировано 16 марта 2014 года.

Литература

- Arthur Trew (Editor), Greg Wilson (Editor). Past, Present, Parallel: A Survey of Available Parallel Computer Systems. — Springer, 1991. — 392 p. — ISBN 9783540196648. (англ.) - книга о супер- 90-ых XX века

Ссылки

- Компьютеры MP-серии

- http://home.wlu.edu/~whaleyt/classes/parallel/topics/maspar/maspar.html

- http://www.phy.ornl.gov/csep/CSEP/MP2/MP2.html Архивная копия от 18 мая 2008 на Wayback Machine

- http://www.bearcave.com/misl/misl_tech/venture_capital.html

- http://www.netlib.org/utk/papers/advanced-computers/mp-1.html