Троичный триггер

Троичный триггер (ternary trigger, ternary latch, ternary flip-flop) — электронное, механическое, пневматическое, гидравлическое, оптическое или другое устройство, имеющее три устойчивых состояния, возможность переключения из любого одного из трёх устойчивых состояний в любое из двух других устойчивых состояний и возможность определения, в каком из трёх устойчивых состояний находится это устройство. Например, троичная ячейка памяти, с возможностью записи и чтения (записанных) троичных кодов (чисел) в ней.

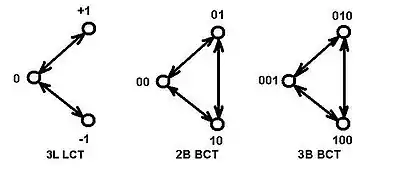

Граф троичных триггеров в физических троичных системах 3B BCT ("трёхпроводной") и 2B BCT ("двухпроводной") — треугольник с двухсторонними переходами от любой вершины к любой другой вершине.

Граф же троичных триггеров в физической троичной системе 3L LCT ("однопроводной") не имеет прямых переходов из -1 в +1 и из +1 в -1, а эти переходы совершаются через прохождение через "0" на 1/3 длительности фронта переключения, что приводит к ложным срабатываниям в последующих логических элементах в более, чем однокаскадных, схемах. В однокаскадных схемах с индикаторами, из-за инерционности зрения, мельтешения из-за этих переходов не видно.

Реверсивный счётчик на 3 и реверсивный регистр сдвига на 3 также являются троичными триггерами.

Троичные триггеры могут быть построены[1]:

1. на двухуровневых логических элементах в двухуровневой трёхбитной системе троичных логических элементов (3Bit BinaryCodedTernary, 3B BCT, «трёхпроводной»),

2. на двухуровневых логических элементах в двухуровневой двухбитной системе троичных логических элементов (2Bit BinaryCodedTernary, 2B BCT, «двухпроводной») и

3. не очень хорошего качества на трёхуровневых логических элементах в трёхуровневой системе троичных логических элементов (3-Level LevelCodedTernary, 3L LCT, «однопроводной»).

История

В 1956—1958 годах Николай Петрович Брусенцов с группой единомышленников (Механико-математический факультет МГУ) построил первую серийную электронную троичную ЭВМ с позиционной симметричной троичной системой счисления Сетунь.

В 1970 г. Брусенцов из МГУ построил электронную троичную ЭВМ Сетунь-70.

Известный советский компьютерный специалист профессор Д. А. Поспелов писал: «Барьеры, стоящие на пути приложения троичной симметричной системы счисления в компьютерах, являются препятствиями технического порядка. До сих пор не разработаны экономичные и эффективные элементы с тремя устойчивыми состояниями. Как только такие элементы будут разработаны, бо́льшая часть компьютеров универсального типа и многие специальные компьютеры по всей вероятности будут разработаны таким образом, чтобы они функционировали в троичной симметрической системе счисления».

Известный американский учёный Дональд Кнут выражал мнение, что «замена двоичного триггера („flip-flop“) на троичный триггер („flip-flap-flop“) в один прекрасный день обязательно произойдёт».[2](«Flip-flop» означает двухступенчатость, «flip-flap-flop» — трёхступенчатость, Кнут же думал, что «flip-flop» означает двоичность (двухзначность), а «flip-flap-flop» — троичность (трёхзначность)).

Применение

Механический троичный счетный триггер применяется в однокнопочных секундомерах.

Элементы и узлы троичных ЭВМ

Подключение относительно простой логики на входе трёхбитного троичного триггера позволяет создать трёхбитный троичный D-триггер с тремя D-входами (троичный D-триггер)[1].

Также возможны трёхбитные троичные аналоги двоичных T-триггеров, троичные регистры данных, троичные полусумматоры, троичные полные сумматоры, троичные арифметико логические устройства (АЛУ), троичные процессоры, троичная статическая оперативная память (SRAM), троичные микроконтроллеры, троичные компьютеры, троичные микроЭВМ.

Преимущества и недостатки

Быстродействие

За один такт один разряд в троичных системах передаёт один троичный разряд (трит), имеющий три состояния, один разряд в двоичных системах передаёт один бит, имеющий два состояния, то есть один троичный разряд передаёт в 3/2=1,5 (полтора) раза больше чисел (кодов), чем один двоичный разряд.

При использовании трёхбитных и двухбитных триггеров число переключений триггеров, в среднем, такое же, как и в трёхуровневых триггерах, но на выходе трёхбитных и двухбитных триггеров частота переключений в отдельных линиях B2, B1 и B0 на 1/3 меньше, чем в трёхуровневом триггере.

При использовании в трёхбитной и в двухбитной системах обычных двоичных триггеров частота переключения в линиях B2, B1 и B0 на 1/3 меньше, чем в трёхуровневом триггере, то есть применение в троичных трёхбитной и двухбитной системах обычных двоичных триггеров и троичных триггеров на обычных двоичных триггерах позволяет применять логические элементы на 1/3 менее высокочастотные, чем в трёхуровневой однопроводной троичной системе.

Аппаратные затраты

В большинстве случаев при построении логических схем на троичных триггерах аппаратные затраты увеличиваются приблизительно в 2 раза по сравнению с обычными двоичными триггерами и только в очень редких случаях, при решении задач имеющих троичность (Задача «Светофор»[3]), удаётся немного уменьшить аппаратные затраты.

Надёжность

Так как двухуровневые трёхбитные троичные триггеры могут работать и в трёхбитном и в двухбитном режимах, то, в случае обрыва одной из трёх выходных линий (проводников), можно перейти на двухбитный режим, что повышает надёжность устройств на этих триггерах.

В трёхбитном режиме, при обрыве одного из трёх выходных проводников, по уровням на оставшихся двух проводниках возможно полное аппаратное или программное восстановление трёхбитного кода.

Конструкция

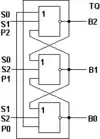

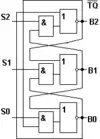

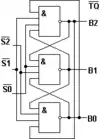

Система обратных связей у всех триггеров одинаковая. Выход каждого из трёх элементов соединяется со входами двух других элементов. В триггерах на трёх элементах 3ИЛИ-НЕ и на трёх элементах 3И-НЕ три входных сигнала подаются на три входа трёх элементов и «землю». Триггеры на трёх элементах 3ИЛИ-НЕ и на трёх элементах 3И-НЕ переключаются подачей сигнала переключения на два из трёх входов. В триггерах на элементах 4И-НЕ (SN7420, К155ЛА1[4], 164ЛА8, К176ЛА8, CD4012, 564ЛА8, К561ЛА8, CD4012A, К555ЛА1) и 4ИЛИ-НЕ (164ЛЕ6, К176ЛЕ6, CD4002, 564ЛЕ6, К561ЛЕ6, CD4002A, КР1561ЛЕ6, CD4002B[5]) оставшиеся 6 входов объединяются в три пары, каждая из трёх пар подключена к двум элементам. Три входных сигнала подаются на три объединённые пары и «землю». Триггеры на трёх элементах 4И-НЕ и на трёх элементах 4ИЛИ-НЕ переключаются подачей сигнала переключения на одну из трёх пар. На выходе триггеров три выходные шины и «земля» (общая), подобно трёхфазной электрической сети.

Трёхразрядный одноединичный троичный триггеры на трёх элементах 2ИЛИ-НЕ и трёхразрядный однонулевой троичный триггер на трёх элементах 2И-НЕ целесообразно использовать в ячейках троичной статической сверхоперативной памяти (троичной SRAM).

Так как при «закреплении» уровня хранения на третьем входе монтажной «1» или монтажным «0» эти триггеры работают как обычный двоичный асинхронный RS-триггер, то эти триггеры в троичной цифровой электронике являются троичными аналогами двоичного асинхронного RS-триггера.

- Входы и выходы

В троичном аналоге RS-триггера три входа: S0 (Set0) — установка в 0 (аналог R-входа), S1 (Set1) — установка в 1 (аналог S-входа), S2 (Set2) — установка в 2 (без аналога) и «земля», и три выхода: Q0 — выход инвертора 0 (аналог Q), Q1 выход инвертора 1 (аналог инверсного Q) и Q2 выход инвертора 2 (без аналога) и «земля».

Двухуровневые троичные триггеры

Двухуровневые троичные триггеры строятся на двухуровневых элементах, а троичность работы достигается с помощью системы обратных связей. Двухуровневые троичные триггеры могут быть двухбитными (двухпроводная двухуровневая троичная система) и трёхбитными (трёхпроводная двухуровневая троичная система).

Двухуровневые двухпроводная и трёхпроводная троичные системы более помехоустойчивы, чем трёхуровневая однопроводная троичная система, так как трёхуровневая однопроводная система работает до относительной ЭДС сигнала помехи до Uп/4=0,25 (до 25 % от Uп), а двухуровневые двухпроводная и трёхпроводная троичные системы работают до относительной ЭДС сигнала помехи до Uп/2=0,5*Uп (до 50 % от Uп).

Двухуровневые 2-разрядные

Одну из множества возможных троичных двухбитных двухпроводных систем кодирования («-»={00}, «0»={01}or{10}, «+»={11}) предложил Carl W. Nelson, Jr. в 1969 г.[6]. Двухбитные двухуровневые троичные триггеры работают в троичной двухбитной двухпроводной системе кодирования {00}, {01}, {10} и имеют трёхбитный или двухбитный вход и двухбитный выход.

В качестве двухбитного троичного триггера можно использовать двухуровневые трёхбитные троичные триггеры в двухбитном режиме (с отключенным выходом TQB2).

Двухуровневые трёхбитные

Трёхбитные двухуровневые (трёхфазные[7]) троичные триггеры имеют однозначный трёхбитный вход и однозначный трёхбитный выход. Двухуровневость позволяет строить однозначные трёхбитные троичные триггеры на обычных элементах двухуровневых логик (РТЛ, ДТЛ, ТТЛ, ЭСЛ, МОП, КМОП и др.).

Известны нижеследующие однозначные трёхбитные троичные триггеры:

- Троичный трёхбитный одноединичный триггер на трёх логических элементах 2ИЛИ-НЕ (функция f2,1,0110)[8].

- Однонулевой трёхбитный троичный триггер на трёх логических элементах 2И-НЕ (функция f2,1,0710).

- Одноединичный трёхбитный троичный триггер на трёх логических элементах 3ИЛИ-НЕ (функция f3,1,110) (триггер с сайта А. П. Стахова)[9](К155ЛЕ4, SN7427).

- Однонулевой трёхбитный троичный триггер на трёх логических элементах 3И-НЕ (функция f3,1,12710) (К155ЛА4, SN7410).

- Трёхбитный одноединичный триггер 3х2ИЛИ-НЕ+3х2И Л. К. Бакстера Larry K. Baxter, Lexington, Mass. Assignee: Shintron Company, Inc., Cambridge, Mass. US Patent 3,764,919 Oct. 9, 1973 Filed: Dec. 22, 1972 Fig.5 с инверсным выходом.

- Триггер 3х2И-НЕ+3х2ИЛИ-НЕ Л. К. Бакстера (Larry K. Baxter, Lexington, Mass. Assignee: Shintron Company, Inc., Cambridge, Mass. US Patent 3,764,919 Oct. 9, 1973 Filed: Dec. 22, 1972 Fig.3) с инверсным входом.

- Троичный трёхбитный одноединичный триггер на трёх логических элементах 4ИЛИ-НЕ А.Турецки[10], который в патенте Larry K. Baxter, Lexington, Mass. Assignee: Shintron Company, Inc., Cambridge, Mass. US Patent 3,764,919 Oct. 9, 1973 Filed: Dec. 22, 1972 Fig.2 уже упоминается как широко известный.

- Однонулевой трёхбитный троичный триггер на трёх логических элементах 4И-НЕ (применён в тристабильной ячейке памяти Takashi Nanya, Tokyo, Japan Assignee: Nippon Electric Company, Limited, Tokyo, Japan US Patent 3,893,086 July 1, 1975 Filed: Dec. 11, 1973 Fig.2. Блок 1) (К155ЛА1, SN7420), подобный триггер с немного усложнённой схемой управления применён в регистре сдвига описанном в патенте "«SU374663 Asynchronous shift register», В. П. Морин и Е. Е. Попов.

- Трёхбитный троичный триггер на трёх логических элементах 2И-2И-2ИЛИ-НЕ (патент SU661606 Memory cell for buffer register. А. И. Бахштаб, В. И. Варшавский, В. Б. Мараховский, В. А. Песчанский, Л. Я. Розенблюм, Н. А. Стародубцев и Б. С. Цирлин).

- Трёхбитный троичный триггер на трёх логических элементах 2И-4ИЛИ-НЕ (АС СССР 599332 25.12.76 Троичный триггер. Н. Г. Коробков, И. Н. Корнет, П. Н. Дмитриев, Л. В. Коробкова, В. И. Гордиенко и В. Д. Близнюк. Харьковский авиационный институт)[11]

Трёхуровневые троичные триггеры

Троичные триггеры на трёхуровневых элементах.

В трёхуровневых элементах трём состояниям соответствуют три уровня напряжения — отрицательное, ноль, положительное, (низкое, среднее, высокое).

В работе[12] на рис.9 приведена схема «троичного статического триггера» на двух трёхуровневых инверторах. Этот триггер имеет три состояния (-1,+1), (+1,-1) и (0,0), но не имеет вращения, а качается как качели или весы.

Схемы троичных трёхуровневых триггеров приведены также в[13] и[14].

Смешанные троичные триггеры

- С двухуровневым (трёхфазным) входом и с трёхуровневым (однофазным) выходом

- С трёхуровневым (однофазным) входом и с двухуровневым (трёхфазным) выходом

На сайте[15] приводится проект смешанного троичного аналога двоичного тактируемого D-триггера с последовательным тактируемым трёхуровневым D-входом и с параллельным двухуровневым (трёхфазным) выходом, состоящий из 11 блоков, от 3 до 5 транзисторов в каждом блоке, то есть, как минимум 33 транзистора на один троичный трёхуровневый D-триггер.

В «Приёмник троичного кода»[16] приводится схема и описание приёмника последовательных трёхуровневых троичных разрядов в «троичном полярном коде» и преобразования их в параллельные двоичные двухразрядные троичные разряды, который является троичным триггером с однолинейным трёхуровневым входом и с двухлинейным двухразрядным выходом с демультиплексором.

Троичные триггеры данных (D-триггеры)

- Триггер Robert C. Braddock USPat.3,662,193 May 9, 1972, Filed May 24, 1971[17] ссылка на прототип из журнала «Electronic Design»,May 10, 1966, раздел «Ideas for Design»

- Троичные триггеры данных (D-триггеры) приведены на странице Троичные триггеры.

Троичные счётные триггеры (Т-триггеры)

- Троичный счётный триггер. АС СССР 764138 27.11.78 Н. Г. Коробков, В. И. Гордиенко, Л. В. Коробкова, Н. Т. Березюк и К. К. Фурманов. Харьковский авиационный институт.[18]

- Троичный счётный триггер. АС СССР 780207 26.12.78 Н. Г. Коробков, Л. В. Коробкова, А. Е. Лебеденко, и К. К. Фурманов. Харьковский авиационный институт им. Н. Е. Жуковского.[19]

- Троичный счётный триггер. SU 1078632 24.12.82 Н. Г. Коробков, Л. В. Коробкова, А. Е. Лебеденко и К. К. Фурманов. Харьковский авиационный институт им. Н. Е. Жуковского.[20]

- Троичный счётный триггер. SU 1188887 28.02.84 Б. С. Цирлин. Институт социально-экономических проблем АН СССР.[21]

- Троичный счётный триггер. SU 1422405 21.01.87 А. С. Галкин, В. П. Грибок, Л. Б. Лимановская и В. О. Твердохлебова[22]. При проверке модели троичного счётного триггера на элементах ИЛИ-НЕ в логическом симуляторе реального времени Atanua триггер оказался работоспособным.

- Троичные счётные триггеры приведены на странице Троичные триггеры и на странице Троичные трёхбитные счётные триггеры (T-триггеры).

- Экономичный трёхбитный (3B BCT UU) троичный счётный триггер (Т-триггер)[23]

См. также

- Троичная система счисления

- Троичный разряд

- Троичная логика

- SRAM (память)

- Троичная SRAM (память)

- Троичная DRAM

- Троичный компьютер

- Троичные АЦП

- Троичные алгоритмы

- Троичный поиск

- Триггер

- Регистр (цифровая техника)

- Счётчик (электроника)

- Сумматор#Троичный сумматор

- Троичный регистр

- Троичная ячейка памяти (перенести содержимое)

Литература

- Гурвич И. С. Многоустойчивые потенциальные схемы,-«Приборы и системы управления», 1968, № 10. АС СССР 599332

- Бухреев И. Н. и др. «Микроэлектронные схемы цифровых устройств». М., «Сов. радио», 1975, с.215, рис.5.51. АС СССР 599332

- Патент США № 3508033 1970

- АС СССР № 319078 1971

- АС СССР № 851785 1979

Ссылки

- Куликов А. С. Троичные триггеры

- Александр Кушнеров. Троичная цифровая техника. Ретроспектива и современность. // Университет им. Бен-Гуриона, Беэр-Шева, Израиль. 28.10.05

- Микросхема нового усилителя тока работающая в троичной системе.

- Prosser, F. Wu, X. Chen, X. Computers and Digital Techniques, IEE Proceedings E. Sep 1988. Volume: 135, Issue: 5, On page(s): 266—272. «CMOS ternary flip-flops and their applications» Dept. of Comput. Sci., Indiana Univ., Bloomington, IN, USA

- Zhuang, N. Wu, H. Electronics Letters. 19 July 1990 Volume: 26, Issue: 15. On page(s): 1145—1146. «Novel ternary JKL flip-flop» Dept. of Electr. Eng., Hangzhou Univ., Zhejiang, China.

- Стив Грабб. Стив Грабб. Проект элементов и узлов троичного компьютера (англ.)

Примечания

- Троичные триггеры

- «Троичный принцип» Николая Брусенцова. (недоступная ссылка). Дата обращения: 5 июня 2008. Архивировано 11 июня 2008 года.

- Экономичность троичной трёхбитной системы троичных логических элементов (3B BCT) на примере задачи «Светофор»

- Транзисторно-транзисторная логика

- Справочник по низкочастотным КМОП микросхемам

- US Patent 3,641,327 Feb. 8, 1972 Filed: Aug. 13, 1969

- Д. А. Поспелов. Логические методы анализа и синтеза схем. Издание третье, переработанное и дополненное. «Энергия» Москва 1974. Стр.352. Определение 9-1.

- Using CMOS gates/US5815436 Multi-level nonvolatile semiconductor memory Такая же схема, не являющаяся предметом патентования, приведена в патенте US5815436 Sep. 29, 1998 Multi-level nonvolatile semiconductor memory device having improved programming level and read/write multi-level data circuits. Tomoharu Tanaka, Hiroaki Hazama, Yokohama, Japan

- Троичный триггер («flip-flap-flop») (недоступная ссылка). Дата обращения: 7 марта 2008. Архивировано 3 марта 2008 года.

- A.Turecki US Pat. 3,508,033 April 21, 1970. Filed Jan. 17, 1967 Fig.2.

- http://www.ee.bgu.ac.il/~kushnero/ternary/Binary%20coded%20ternary/SU599332%20Fast%20ternary%20trigger.pdf Троичный триггер. АС СССР 599332 Заявлено 25.12.76

- Троичная цифровая техника. Перспектива и современность. 28.10.05 Александр Кушнеров, Университет им. Бен-Гуриона, Беэр-Шева, Израиль.

- Figure Архивная копия от 12 мая 2010 на Wayback Machine D.45. PZN tri-flop, from Mouftah’s Image:Mouftah-8a-PZN Tri-flop.png from Mouftah’s patent[15]

- http://jeff.tk:81/wiki/Trinary/Circuits#D.5.2._PZN_Tri-Flop Архивная копия от 12 мая 2010 на Wayback Machine Figure D.48. Mouftah’s clocked PZN tri-flop, from Image:Mouftah-9-Clocked PZN Tri-flop.png

- trinary.cc

- «Приёмник троичного кода» М. А. Буркова, К. А. Гусакова, Озёрский технологический институт (филиал) МИФИ, Научная сессия МИФИ-2007. Том 1.

- TRI-STABLE CIRCUIT (недоступная ссылка)

- Троичный счётный триггер АС СССР 764138 Заявлено 27.11.78

- Троичный счётный триггер АС СССР 780207 Заявлено 26.12.78

- Троичный счётный триггер АС СССР 1078632 Заявлено 24.12.84

- Троичный счётный триггер (его варианты) АС СССР 1188887 Заявлено 28.02.84

- Троичный счётный триггер АС СССР 1422405 Заявлено 21.01.87

- Экономичный трёхбитный (3B BCT UU) троичный счётный триггер (Т-триггер)