Троичная ячейка памяти

Троичная ячейка памяти используется в электронике, в пневмонике и в других областях.

Традиционно ячейка памяти определяется, как наименьшая часть памяти имеющая свой адрес. При таком определении троичная ячейка памяти может иметь несколько троичных разрядов в зависимости от системы адресации памяти троичной ЭВМ (компьютера).

По элементной основе троичные ячейки памяти могут быть построены

Классификация

Трёхуровневые

В них три потенциала разных уровней (положительный, нулевой, отрицательный) соответствуют трём устойчивым состояниям ячейки

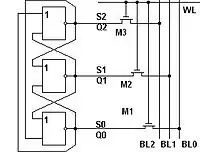

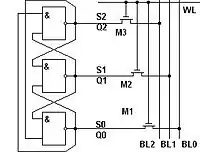

Двухуровневые

В них элементарным устройством является двухуровневый инвертор с двумя потенциалами (высокий, низкий), а троичность работы достигается цепями обратных связей между тремя двухуровневыми инверторами. Такая ячейка памяти называется троичный двухуровневый триггер.

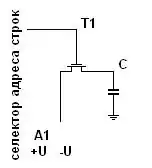

Троичная DRAM

Троичная DRAM построена, подобно двоичной DRAM, на элементе с одним конденсатором и одним аналоговым ключом, работающим и с положительными и с отрицательными сигналами, но с биполярным зарядом конденсатора. Положительный заряд соответствует одному из трёх состояний, отрицательный второму, а «0» — третьему состоянию. В схемах считывания-регенерации вместо одного компаратора, который делит весь диапазон амплитуд на две части, два компаратора, которые делят весь диапазон амплитуд на три части. Схемы записи при этом подают на ячейки и положительное и отрицательное напряжение.

Элемент такой троичной ячейки DRAM показан на рисунке справа.

При одинаковом числе конденсаторов ёмкость троичной трёхуровневой DRAM увеличивается в 1,58 раз.

При этом трёхуровневая DRAM, по сравнению с двухуровневой DRAM имеет в 1,5 раза меньшее быстродействие.

При одинаковом размахе напряжений трёхуровневая DRAM имеет меньшую помехоустойчивость.

Для достижения одинаковой с двухуровневой DRAM помехоустойчивости нужно увеличить размах напряжений, что потребует увеличение максимального допустимого напряжения почти всех элементов микросхемы DRAM.

Все эти свойства определяют область её применения: в 1,5 раза более медленные, с в 1,5 раза меньшей помехоустойчивостью, DRAM с в 1,58 раз большей ёмкостью[2].

См. также

- Троичная логика

- Троичный разряд

- Троичный триггер

- Троичная ЭВМ