Счётчик (электроника)

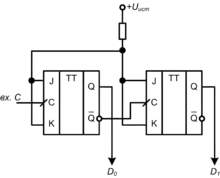

Счётчик числа импульсов — устройство, на выходах которого получается двоичный или двоично-десятичный код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Классификация

Счётчики классифицируют:

- по числу устойчивых состояний триггеров

- на двоичных триггерах

- на троичных триггерах[1]

- на n-ичных триггерах

- по модулю счёта:

- двоично-десятичные (декада);

- двоичные;

- с произвольным постоянным модулем счёта;

- с переменным модулем счёта;

- по направлению счёта:

- суммирующие;

- вычитающие;

- реверсивные;

- по способу формирования внутренних связей:

- с последовательным переносом;

- с ускоренным переносом;

- с параллельным ускоренным переносом;

- со сквозным ускоренным переносом;

- с комбинированным переносом;

- кольцевые;

- по способу переключения триггера:

- синхронные;

- асинхронные;

- Счётчик Джонсона[2]

Двоичные счётчики

Схему двоичного счётчика можно получить с помощью формального синтеза, однако более наглядным путём представляется эвристический. Таблица истинности двоичного счётчика — последовательность двоичных чисел от нуля до , где n — разрядность счётчика. Наблюдение за разрядами чисел, составляющих таблицу, приводит к пониманию структурной схемы двоичного счётчика. Состояния младшего разряда при его просмотре по соответствующему столбцу таблицы показывают чередование нулей и единиц вида 01010101…, что естественно, так как младший разряд принимает входной сигнал и переключается от каждого входного воздействия. В следующем разряде наблюдается последовательность пар нулей и единиц вида 00110011… . В третьем разряде образуется последовательность из четвёрок нулей и единиц 00001111… и т. д. Из этого наблюдения видно, что следующий по старшинству разряд переключается с частотой, в два раза меньшей, чем данный.

Известно, что счётный триггер делит частоту входных импульсов на два. Сопоставив этот факт с указанной выше закономерностью, видим, что счётчик может быть построен в виде цепочки последовательно включённых счётных триггеров. Заметим, кстати, что согласно ГОСТу входы элементов изображаются слева, а выходы справа. Соблюдение этого правила ведёт к тому, что в числе, содержащемся в счётчике, младшие разряды расположены левее старших.

Двоичные счётчики с параллельным переносом и соседним кодированием

Выше рассмотрены схемы двоичных последовательных счётчиков, то есть таких счётчиков, в которых при изменении состояния определённого триггера возбуждается последующий триггер, причём триггеры меняют свои состояния не одновременно, а последовательно. Если в данной ситуации должны изменить свои состояния n триггеров, то для завершения этого процесса потребуется n интервалов времени, соответствующих времени изменения состояния каждого из триггеров. Такой последовательный характер работы является причиной двух недостатков последовательного счётчика: меньшая скорость счёта по сравнению с параллельными счётчиками и возможность появления ложных сигналов на выходе схемы. В параллельных счётчиках синхронизирующие сигналы поступают на все триггеры одновременно.

Последовательный характер переходов триггеров счётчика является источником ложных сигналов на его выходах. Например, в четырёхразрядном счётчике, ведущем счёт в обычном четырёхразрядном двоичном коде с «весами» разрядов 8-4-2-1, при переходе от состояния к состоянию на выходе появится следующая последовательность состояний:

Это означает, что при переходе из состояния 7 в состояние 8 на входах счётчика на короткое время появятся коды, соответствующие состояниям 6; 4; 0. Смена этих промежуточных состояний может вызвать ложную работу других логических схем, например, если к такому счётчику подключён дешифратор, то на его выходах 0, 4, 6 могут кратковременно возникнуть активные состояния, которые могут ложно изменить состояния подключённых к ним по входам других триггеров — это нежелательное явление называют логическими «гонками» или «гонками сигналов». Исключить гонки можно, применяя счётчики с соседним или противогоночным кодированием состояний, например, считающие в рефлексивном коде Грея.

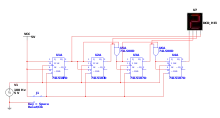

С целью уменьшения времени протекания переходных процессов можно реализовать счётчик в варианте с подачей входных счётных импульсов одновременно на все триггеры. В этом случае получим счётчик с параллельным переносом.

По схемам счётчиков с параллельным переносом строятся счётчики, задержка переключения одного триггера у которых соизмерима с периодом считаемых импульсов.

Пример. Если задержка переключения одного триггера 30 нс, то при построении счётчика по схеме с последовательным переносом более чем четырёхразрядного, работающего в обычном двоичном коде, при периоде счётных импульсов 120 нс и ниже начнутся сбои счёта, перенос не успевает распространиться по цепочке триггеров до прихода очередного счётного импульса.

В счётчиках с параллельным переносом на информационные входы триггеров подаются сигналы, являющиеся логической функцией состояния счётчика и определяющие конкретные триггеры, которые должны изменить своё состояние при данном входном импульсе. Принцип стробирования сводится к следующему: триггер меняет своё состояние при пропускании очередного импульса синхронизации, если все предыдущие триггеры находились в состоянии логической единицы.

Параллельные счётчики имеют более высокое быстродействие по сравнению с последовательными, поскольку логическая функция от текущего состояния счётчика и счётного импульса поступают на переключающие входы всех триггеров одновременно.

Максимальным быстродействием обладают синхронные счётчики с параллельным переносом, структуру которых найдем эвристически, рассмотрев процессы прибавления единицы к двоичным числам и вычитания её из них.

Счётчики с последовательно-параллельным переносом

В связи с ограничениями на построение счётчиков с параллельным переносом большой разрядности широкое распространение получили счётчики с групповой структурой, или счётчики с последовательно-параллельным переносом. Разряды таких счётчиков разбиваются на группы, внутри которых организуется принцип параллельного переноса. Сами же группы соединяются последовательно с использованием конъюнкторов, формирующих перенос в следующую группу при единичном состоянии всех триггеров предыдущих. При единичном состоянии всех триггеров группы приход очередного входного сигнала создаст перенос из этой группы. Эта ситуация подготавливает межгрупповой конъюнктор к прямому пропусканию входного сигнала на следующую группу.

В наихудшем для быстродействия случае, когда перенос проходит через все группы и поступает на вход последней,

- tУСТ = t • (ĺ — 1) + tГР,

где ĺ — число групп, tГР — время установления кода в группе.

В развитых сериях ИС обычно имеется по 5…10 вариантов двоичных счётчиков, выполненных в виде четырёхразрядных групп (секций). Каскадирование секций может выполняться путём их последовательного включения по цепям переноса, организации параллельно-последовательных переносов или для более сложных счётчиков с двумя дополнительными управляющими входами разрешения счета и разрешения переноса путём организации параллельных переносов и в группах, и между ними.

Особенностью двоичных счётчиков синхронного типа является наличие ситуаций с одновременным переключением всех его разрядов (например, для суммирующего счётчика при переходе от кодовой комбинации 11…1 к комбинации 00…0 при переполнении счётчика и выработке сигнала переноса). Одновременное переключение многих триггеров создаёт значительный токовый импульс в цепях питания ЦУ и может привести к сбою в их работе. Поэтому в руководящих материалах по использованию некоторых БИС/СБИС программируемой логики, в частности, имеется ограничение на разрядность двоичных счётчиков заданной величиной k (например, 16). При необходимости применения счётчика большей разрядности рекомендуется переходить к коду Грея, для которого переходы от одной кодовой комбинации к другой сопровождаются переключением всего одного разряда. Правда, для получения результата счета в двоичном коде придётся использовать дополнительно преобразователь кода, но это является платой за избавление от токовых импульсов большой интенсивности в цепях питания.

См. также

- Декатрон

- Делитель частоты

- Таймер

- Электронный счётчик импульсов

- Сумматор

Примечания

- А.С.Галкин, В.П.Грибок и В.М.Казаков. Кольцевой счётчик на потенциальных логических элементах, Binary coded ternary/АС SU1466009.

- Счётчики. Счётчик Джонсона.