Serial Peripheral Interface

SPI (англ. Serial Peripheral Interface, SPI bus — последовательный периферийный интерфейс, шина SPI) — последовательный синхронный стандарт передачи данных в режиме полного дуплекса, предназначенный для обеспечения простого и недорогого высокоскоростного сопряжения микроконтроллеров и периферии. SPI также иногда называют четырёхпроводным (англ. four-wire) интерфейсом.

В отличие от стандартного последовательного порта (англ. standard serial port), SPI является синхронным интерфейсом, в котором любая передача синхронизирована с общим тактовым сигналом, генерируемым ведущим устройством (процессором). Принимающая (ведомая) периферия синхронизирует получение битовой последовательности с тактовым сигналом. К одному последовательному периферийному интерфейсу ведущего устройства-микросхемы может присоединяться несколько микросхем. Ведущее устройство выбирает ведомое для передачи, активируя сигнал «выбор кристалла» (англ. chip select) на ведомой микросхеме. Периферия, не выбранная процессором, не принимает участия в передаче по SPI.

Интерфейс

В SPI используются четыре цифровых сигнала:

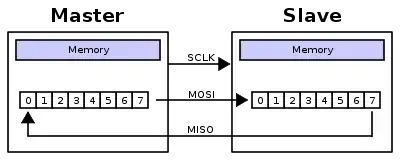

- MOSI — выход ведущего, вход ведомого (англ. Master Out Slave In). Служит для передачи данных от ведущего устройства ведомому.

- MISO — вход ведущего, выход ведомого (англ. Master In Slave Out). Служит для передачи данных от ведомого устройства ведущему.

- SCLK или SCK — последовательный тактовый сигнал (англ. Serial Clock). Служит для передачи тактового сигнала для ведомых устройств.

- CS или SS — выбор микросхемы, выбор ведомого (англ. Chip Select, Slave Select).

Конкретные имена портов интерфейса SPI могут различаться в зависимости от производителя аппаратных средств, при этом возможны следующие варианты:

- MISO: SOMI, SDO (на устройстве), DO, DON, SO, MRSR;

- MOSI: SIMO, SDI (на устройстве), DI, DIN, SI, MTST;

- SCLK: SCK, CLK, SPC (SPI serial port clock);

- SS: nCS, CS, CSB, CSN, NSS, nSS, STE, SYNC.

Синхронизация в SPI

Частота следования битовых интервалов в линиях передачи данных определяется синхросигналом SCK, который генерирует ведущее устройство, ведомые устройства используют синхросигнал для определения моментов изменения битов на линии данных, при этом ведомые устройства никак не могут влиять на частоту следования битовых интервалов. Как в ведущем устройстве, так и в ведомом устройстве имеется счетчик импульсов синхронизации (битов). Счетчик в ведомом устройстве позволяет последнему определить момент окончания передачи пакета. Счетчик сбрасывается при выключении подсистемы SPI, такая возможность всегда имеется в ведущем устройстве. В ведомом устройстве счетчик обычно сбрасывается деактивацией интерфейсного сигнала SS.

Так как действия ведущего и ведомого устройства тактируются одним и тем же сигналом, то к стабильности этого сигнала не предъявляется никаких требований, за исключением ограничения на длительность полупериодов, которая определяется максимальной рабочей частотой более медленного устройства. Это позволяет использовать SPI в системах с низкостабильной тактовой частотой, а также облегчает программную эмуляцию ведущего устройства.

Прием и передача данных в SPI

Передача осуществляется пакетами. Длина пакета, как правило, составляет 1 байт (8 бит), при этом известны реализации SPI с иной длиной пакета, например, 4 бита. Ведущее устройство инициирует цикл связи установкой низкого уровня на выводе выбора подчиненного устройства (SS) того устройства, с которым необходимо установить соединение. При низком уровне сигнала SS:

- схемотехника ведомого устройства находится в активном состоянии;

- вывод MISO переводится в режим «выход»;

- тактовый сигнал SCLK от ведущего устройства воспринимается ведомым и вызывает считывание на входе MOSI значений передаваемых от ведущего битов и сдвиг регистра ведомого устройства.

Подлежащие передаче данные ведущее и ведомое устройства помещают в сдвиговые регистры. После этого ведущее устройство начинает генерировать импульсы синхронизации на линии SCLK, что приводит к взаимному обмену данными. Передача данных осуществляется бит за битом от ведущего по линии MOSI и от ведомого по линии MISO. Передача осуществляется, как правило, начиная со старших битов, но некоторые производители допускают изменение порядка передачи битов программными методами. После передачи каждого пакета данных ведущее устройство, в целях синхронизации ведомого устройства, может перевести линию SS в высокое состояние.

Режимы работы интерфейса SPI

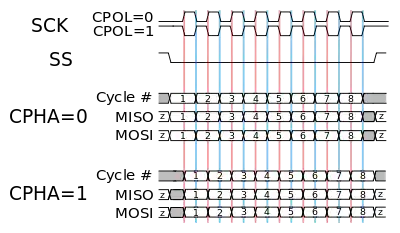

При CPHA = 0 красная вертикальная линия

При CPHA = 1 синяя вертикальная линия

Возможны четыре режима синхронизации. Режим определяется комбинацией бит CPHA и CPOL:

- CPOL = 0 — исходное состояние сигнала синхронизации -- низкий уровень;

- CPOL = 1 — исходное состояние сигнала синхронизации -- высокий уровень;

- CPHA = 0 — выборка данных производится по переднему фронту(переключению) сигнала синхронизации. То есть по переключению из основного в противоположное ему;

- CPHA = 1 — выборка данных производится по заднему фронту(переключению)сигнала синхронизации.То есть по переключению обратно к основному из противоположного;

Для обозначения режимов работы интерфейса SPI принято следующее соглашение:

- режим 0 (CPOL = 0, CPHA = 0);

- режим 1 (CPOL = 0, CPHA = 1);

- режим 2 (CPOL = 1, CPHA = 0);

- режим 3 (CPOL = 1, CPHA = 1).

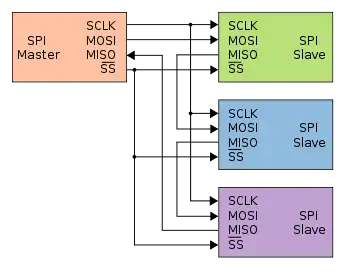

Топология систем связи на базе SPI

В простейшем случае к ведущему устройству подключено единственное ведомое устройство и необходим двусторонний обмен данными. В таком случае используется трехпроводная схема подключения. Интерфейс SPI позволяет подключать к одному ведущему устройству несколько ведомых устройств, причем подключение может быть осуществлено несколькими способами.

Первый способ позволяет реализовать радиальную структуру связи (топология типа «звезда»), его принято считать основным способом подключения нескольких ведомых устройств. В данном случае для обмена более чем с одним ведомым устройством ведущее устройство должно формировать соответствующее количество сигналов выбора ведомого устройства (SS). При обмене данными с ведомым устройством, соответствующий ему сигнал SS переводится в активное (низкое) состояние, при этом все остальные сигналы SS находятся в неактивном (высоком) состоянии. Выводы данных MISO ведомых устройств соединены параллельно, при этом они находятся в неактивном состоянии, а перед началом обмена один из выходов (выбранного ведомого устройства) переходит в активный режим.

Второй способ позволяет реализовать структуру связи типа «кольцо». В данном случае для активации одновременно нескольких ведомых устройств используется один сигнал SS, а выводы данных всех устройств соединены последовательно и образуют замкнутую цепь. При передаче пакета от ведущего устройства этот пакет получает первое ведомое устройство, которое, в свою очередь, транслирует свой пакет следующему ведомому устройству и так далее. Для того, чтобы пакет от ведущего устройства достиг определенного ведомого устройства, ведущее устройство должно отправить еще несколько пакетов.

Преимущества и недостатки интерфейса SPI

Преимущества

- Полнодуплексная передача данных по умолчанию.

- Более высокая пропускная способность по сравнению с I²C или SMBus.

- Возможность произвольного выбора длины пакета, длина пакета не ограничена восемью битами.

- Простота аппаратной реализации:

- Используется только четыре вывода, что гораздо меньше, чем для параллельных интерфейсов.

- Однонаправленный характер сигналов позволяет при необходимости легко организовать гальваническую развязку между ведущим и ведомыми устройствами.

- Максимальная тактовая частота ограничена только быстродействием устройств, участвующих в обмене данными.

Недостатки

- Необходимо больше выводов, чем для интерфейса I²C.

- Ведомое устройство не может управлять потоком данных.

- Нет подтверждения приема данных со стороны ведомого устройства (ведущее устройство может передавать данные «в никуда»).

- Нет определенного стандартом протокола обнаружения ошибок.

- Отсутствие официального стандарта, что делает невозможным сертификацию устройств.

- По дальности передачи данных интерфейс SPI уступает таким стандартам, как UART и CAN.

- Наличие множества вариантов реализации интерфейса.

- Отсутствие поддержки горячего подключения устройств.

Пример программной реализации

Ниже представлен пример программной реализации SPI мастера на языке Си. Линия CS (chip select, выбор микросхемы) должна быть активирована (в большинстве случаев — притянута к низкому уровню), перед тем, как начнётся обмен данными, и деактивирована после окончания обмена. Большинство устройств требуют несколько сеансов передачи с активной линией CS. Эта функция может быть вызвана несколько раз, пока линия активна.

unsigned char SPIBitBang8BitsMode0(unsigned char byte)

{

unsigned char bit;

for (bit = 0; bit < 8; bit++) {

/* записать MOSI по спаду предыдущего тактового импульса */

if (byte & 0x80)

SETMOSI();

else

CLRMOSI();

byte <<= 1;

/* ждём половину тактового периода, перед тем как сгенерировать фронт */

SPIDELAY(SPISPEED/2);

SETCLK();

/* ждём половину тактового периода, перед тем как сгенерировать спад */

SPIDELAY(SPISPEED/2);

/* читаем MISO на спаде */

byte |= READMISO();

CLRCLK();

}

return byte;

}

См. также

Литература

- Болл Стюарт Р. Аналоговые интерфейсы микроконтроллеров. — М.: Додэка-XXI, 2007. — 360 с. — (Программируемые системы). — 2000 экз. — ISBN 978-5-94120-142-6.

- Лапин А.А. Интерфейсы. Выбор и реализация. — М.: Техносфера, 2005. — 168 с. — (Мир электроники). — 5000 экз. — ISBN 5-94836-058-X.