Дешифратор

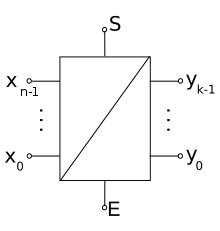

Дешифра́тор (декодер) (англ. decoder) в цифровой электронике — комбинационная схема, преобразующая n-разрядный двоичный, троичный или k‑ичный код в ‑ичный одноединичный код, где — основание системы счисления.

Одноединичный код — последовательность бит, содержащая только один активный бит/трит; остальные биты/триты последовательности неактивны.

Активный бит/трит — бит/трит, равный либо единице, либо нулю (зависит от реализации дешифратор/триты:

- либо равные значению, инверсному (NOT) значению активного бита/трита;

- либо находящиеся в 3-м низкоимпедансном состоянии с высокой нагрузочной способностью или в высокоимпедансном состоянии с очень низкой нагрузочной способностью.

Логический сигнал активен на том выходе, порядковый номер которого соответствует двоичному, троичному или k‑ичному коду.

Двоичный (k=2) дешифратор работает следующим образом:

- на вход дешифратора подаётся двоичное слово из n бит. Количество допустимых входных комбинаций из n бит равно ;

- на выходе у дешифратора формируется двоичное слово из числа битов, меньшего или равного . В выходном слове всегда имеется один активный бит, равный 1 или 0, остальные биты неактивны. Активность 0 или 1 зависит от конкретной реализации дешифратора. Неактивные биты либо все имеют состояние инверсное к активному биту, либо переводятся в 3-е, высокоимпедансное состояние.

Дешифраторы являются устройствами, выполняющими двоичные, троичные или k‑ичные логические функции (операции).

Логические функции двоичного дешифратора

Двоичный дешифратор работает по следующему принципу.

Пусть дешифратор имеет n входов. На входы подаётся двоичное слово . На выходах формируется код , разрядность которого меньше или равна . Активным становится разряд, номер которого равен численному представлению входного слова. Под активностью разряда понимается принятие им значения логической единицы, логического нуля или перевод в высокоимпедансное состояние — отключение; конкретное значение зависит от используемой реализации дешифратора. Остальные разряды остаются неактивными. Максимально возможная разрядность выходного слова равна .

Дешифратор называется полным, если число выходов равно максимально возможной разрядности выходного слова (). Дешифратор называется неполным, если часть входных разрядов не используется (то есть число выходов меньше ).

Например, если для полного двоичного дешифратора (k=2) число входных разрядов n=3, и на вход поступает слово 0102=210, на выходе будет доступно 23=8 бит, из которых активным будет только один — 2-й бит. Этот бит будет равен 1 или 0 (зависит от реализации), а остальные биты будут неактивны (либо будут равны 0 или 1, либо будут находиться в высокоимпедансном состоянии).

Функционирование одноединичного дешифратора, активные выходные сигналы которого принимают значение логической единицы, описывается системой конъюнкций:

…

Часто дешифраторы дополняются входом E (от англ. enable) — «входом разрешения работы» (включения). Если на этот вход поступает активный логический сигнал (единица или ноль), то один из выходов дешифратора переходит в активное состояние, иначе все выходы неактивны вне зависимости от состояния входов.

Функционирование одноединичного дешифратора с дополнительным входом E описывается системой конъюнкций:

…

Обычно микросхемы дешифраторов выполняют с инверсными (NOT) выходами (то есть активный выбранный разряд принимает значение логического нуля).

Двоичное слово на входе дешифратора часто называют адресом.

Одноединичные дешифраторы

Бинарный двоичный одноединичный дешифратор.

Таблица истинности двухвходового двоичного дешифратора с 4 выходами () приведена в таблице:

| x0 | 1 | 0 | 1 | 0 | ||

|---|---|---|---|---|---|---|

| x1 | 1 | 1 | 0 | 0 | Активный выход | Условный номер функции |

| F0 | 0 | 0 | 0 | 1 | F0 | F2,1 |

| F1 | 0 | 0 | 1 | 0 | F1 | F2,2 |

| F2 | 0 | 1 | 0 | 0 | F2 | F2,4 |

| F3 | 1 | 0 | 0 | 0 | F3 | F2,8 |

Трёхвходовый двоичный одноединичный дешифратор

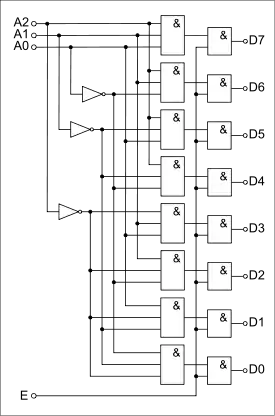

В таблице показаны схема полного трёхвходового двоичного дешифратора, реализованного на логических элементах «И» (AND) и его таблица истинности.

| Логическая схема | Адрес | Разрешение | Состояние выходов | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| A2 | A1 | A0 | E | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| ||||||||||||

| 0 | 0 | 0 | 0 | x | x | x | x | x | x | x | x | |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 0 | x | x | x | x | x | x | x | x | |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 0 | x | x | x | x | x | x | x | x | |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 0 | x | x | x | x | x | x | x | x | |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 0 | x | x | x | x | x | x | x | x | |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 1 | 0 | x | x | x | x | x | x | x | x | |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| Дешифратор, реализованный на логических элементах «И» (AND). | Активное состояние выходов - логическая 1, неактивное - логический 0 х - неактивное состояние всех выходов, для приведённой слева схемы - логический 0. | |||||||||||

Наращивание разрядности дешифраторов

Из логических микросхем, являющихся дешифраторами со входами разрешения, можно строить дешифраторы на большее число входов и выходов. Например, из двух полных трёхвходовых дешифраторов можно построить полный дешифратор на 4 входа и 16 выходов. При этом 3 младших бита входного слова подаются на оба дешифратора, а на вход разрешения одного из них (старшего) 4-й бит слова, на вход разрешения второго дешифратора (младшего) логически инвертированный (NOT) 4-й бит слова.

Примеры применения

- Одноединичный двоичный дешифратор, на вход которого подаётся последовательно возрастающий на единицу двоичный код, формирует на выходе сигнал «бегущий ноль», который широко используется для управления матричными индикаторами, многоразрядными семисегментными индикаторами, для опроса клавиатуры.

- Одноединичный двоичный дешифратор, подключённый к шине адреса микропроцессорной системы, называется дешифратором адреса. Его выходные сигналы, поданные на входы разрешения чтения или записи регистра, микросхемы ОЗУ или ПЗУ, позволяют инициировать «обращение по адресу» к тому или иному периферийному устройству, подключённому к шине данных.

- Специализированный дешифратор (являющийся по сути ПЗУ, которое выдаёт 7-разрядные слова в ответ на поступающий на него 4-разрядный адресный код) применяется для преобразования двоичного кода в отображение десятичных цифр на семисегментных индикаторах.

Обратное преобразование кодов

Обратное преобразование осуществляет шифратор.

См. также

Литература

- Угрюмов Е. П. Цифровая схемотехника. — СПб.: БХВ-Петербург, 2002. — 46 с. — ISBN 5-8206-0100-9

- Шило В. Л. Популярные микросхемы ТТЛ. М., Аргус, 1993, ISBN 5-85549-004-1