R10000

R10000 (кодовое имя «Т5») — RISC-микропроцессор, реализующий набор инструкций MIPS IV. Разработан компанией MIPS Technoligies, Inc. (MTI, позже ставшей подразделением SGI). Главные разработчики — Крис Роуэн и Кеннет С. Йегер. R10000 построен на основе микроархитектуры ANDES (Architecture with Non-sequential Dynamic Execution Scheduling — архитектура с непоследовательным динамическим планированием исполнения).[1] R10000 во многом заменил R8000 в высокопроизводительном сегменте и R4400 в других применениях. MTI является бесфабричной компанией, процессоры R10000 изготавливались NEC и Toshiba. Предыдущие производители микропроцессоров MIPS, IDT и другие не производили R10000, так как это было более дорогим, чем R4000 и R4400.

История

R10000 был представлен в январе 1996 года в версиях с тактовой частотой 175 МГц и 195 МГц. В 1997 году была представлена 150 МГц версия в продуктовой линейке О2, но её вскоре сняли с производства из-за большей популярности 175 МГц модели. R10000 не был доступен в больших объёмах до конца года из-за проблем изготовления. Версия 195 МГц оставалась в дефиците на протяжении 1996 года, и продавалась по цене в 3000 долларов США.[2]

25 сентября 1996 года SGI объявила о том, что R10000 произведенные компанией NEC в марте и конце июля были неисправны, потребляет слишком много тока и приводят к отключению систем во время работы. SGI отозвал системы, использующие около 10 тысяч процессоров R10000, что повлияло на прибыль компании.[3][4]

В 1997 году версия R10000, изготовленная по 0.25 мкм техпроцессу, достигла частоты 250 МГц.

Применения

R10000 использовался в нескольких компьютерных системах:

- SGI:

- NEC, в суперкомпьютере Cenju-4

- Siemens Nixdorf, в серверах, работающих под управлением SINIX

- Tandem Computers, в отказоустойчивых серверах Himalaya

Описание

R10000 имеет суперскалярный дизайн с 4 конвейерами, реализует переименование регистров и применяет внеочередное исполнение инструкций. Дизайн R10000 отличается от предыдущих MIPS микропроцессоров, таких как R4000, который представлял собой скалярный процессор без внеочередного исполнения и опирался в основном на высокие тактовые частоты для получения производительности.

Каждый такт в R10000 может запрашиваться до четырёх инструкции из кэша инструкций. Эти инструкции декодируются и затем, в зависимости от типа, помещаются в одну из очередей исполнения: целочисленных операций, команд над числами с плавающей запятой или инструкций загрузки/сохранения. Блок декодирования использует подсказки типа команд, подготовленные кэшем инструкций: каждая команда помечается пятью битами для определения, в какие исполнительные устройства направить инструкцию, и оптимизации процесса декодирования.

Каждая из очередей инструкций может принять до четырёх инструкций от декодера. Инструкции из очередей выдаются на исполнение в соответствующий исполнительный конвейер динамически, в зависимости от готовности их операндов и доступности ресурсов. Каждая из очередей, за исключением очереди операций загрузки/сохранения может выдавать до двух инструкций за такт. В очереди загрузки/сохранения может запускаться только одна инструкция. Таким образом, R10000 может исполнять до пяти команд в такт.

Блок целочисленных операций

Целочисленное устройство состоит из целочисленного регистрового файла и трех конвейеров: два для исполнения целочисленных операций, и один для операций с памятью. Целочисленный регистровый файл имеет ширину 64 бита и содержит 64 регистра, из которых 32 являются архитектурными и 32 используются для переименования регистров. Регистровый файл имеет семь портов чтения и три порта записи. Оба целочисленных конвейера имеют блоки сумматора и логических операций. Однако только первый конвейер предоставляет устройство быстрого сдвига (barrel shifter) и оборудование для подтверждения предсказания ветвления. Второй конвейер используется для доступа к умножителю и делителю. Умножитель конвейеризован, имеют шеститактную задержку для 32-разрядных целых чисел, и задержку в десять тактов для 64-разрядных целых чисел. Блок деления не конвейеризован. Деление производится по не восстанавливающему алгоритму, который выдает по одному биту за такт. Задержка деления для 32-битных и 64-битных целых составляет 35 и 67 тактов соответственно.

Блок операций с плавающей запятой

Блок вычислений с плавающей запятой (FPU) состоит из четырёх функциональных устройств: сумматора, умножителя, блока деления и блоки извлечения квадратного корня. Сумматор и умножитель конвейеризованы, деление и блок квадратного корня — не конвейеризованы. Сложение и умножение имеют задержку в три такта и могут принимать новую инструкцию каждый такт. Блок деления имеет задержку 12 или 19 тактов в зависимости от разрядности данных, для одинарной точности и двойной соответственно.

Блок квадратного корня блок выполняет операции извлечения квадратного корня и обратного квадратного корня. Инструкции квадратного корня имеют задержку в 18 и 33 такта для одинарной и двойной точности соответственно. Новая инструкция квадратного корня может выдаваться в блок каждые 20 или 35 тактов для одинарной и двойной точности соответственно. Обратные квадратные корни вычисляются за 30 или 52 тактов для одинарной (32-бит) и двойной точности (64-бит) соответственно.

Регистровый файл для чисел с плавающей запятой содержит шестьдесят четыре 64-разрядных регистра, из которых 32 — архитектурные и 32 — для переименования регистров. Сумматор имеет собственные выделенные порты чтение и записи, для остальных блоков используется разделяемый порт.

Блоки деления и квадратного корня используют алгоритм SRT. MIPS IV имеет команду умножения-сложения. Данная инструкция реализована в R10000 при помощи байпаса — результат умножения может быть доставлен в обход регистрового файла непосредственно в конвейер сумматора в качестве операнда. Поэтому данная реализация не является совмещенным умножением-сложением и имеет четыре такта задержки.

Кэш-память

R10000 использует две сравнительно больших кэша, реализованных на том же чипе: 32 КБ кэш инструкций и 32 КБ кэш данных. Кэш инструкций — 2-х канальный множественно-ассоциативный, использует строки в 128 байтов. Инструкции частично декодируется путем добавления четырёх битов к каждой инструкции (размер одной инструкции 32 бита).

32 КБ кэш данных является двухпортовым с двукратным чередованием. Он состоит из двух 16 КБ банков, и каждый банк использует двух-канальную ассоциативность. Кэш использует строки размером 64 байта, протокол write-back, индексируется виртуально и тегируется физически. Такой подход позволяет производить индексирование в том же такте и поддерживать когерентность с кэшем L2.

Внешний кэш L2 является общим для инструкций и данных и может иметь размер от 512 КБ до 16 МБ. Он реализуется на базе синхронной статической памяти (SSRAM). Доступ к кэшу осуществляется через 128-битную шину, защищенную 9-битным кодом коррекции ошибок (ECC). Кэш и шина работают на тактовой частоте процессора R10000. На 200 МГц, шина имеет пиковую пропускную способность 3.2 ГБ/с. Кэш использует двух-канальную ассоциативность, но для сокращения числа контактов R10000 прогнозирует канал для обращения.

Адресация

MIPS IV является 64-битной архитектурой, но R10000 не реализует полное физическое или виртуальное адресное пространство для снижения себестоимости. Процессор предлагает 40-битную физическую адресацию и 44-разрядную виртуальную адресацию, что позволяет адресовать до 1 ТБ физической памяти и до 16 ТБ виртуальной памяти.

Системная шина Avalance

В качестве системной шины используется Avalance — 64-разрядная шина, работающая на частотах до 100 МГц. Шина Avalance мультиплексирует адреса и данные, поэтому из максимальной теоретической пропускной способности 800 МБ/с при частоте 100 МГц для передачи данных доступно лишь 640 МБ/с, так как часть тактов используется для передачи адресов.

Встроенный контроллер системного интерфейса поддерживает реализацию симметричных многопроцессорных систем (SMP) размером до четырёх микропроцессоров включительно. Применение внешних контроллеров позволяет создавать системы из сотен процессоров R10000. Примером такой системы является SGI Origin 2000.

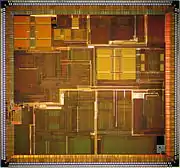

Изготовление

Процессор R10000 насчитывает около 6,8 миллионов транзисторов, из которых примерно 4,4 миллиона составляют реализацию кэшей первого уровня.[5] Чип имеет размеры 16.64 на 17.934 мм с общей площадью 298.42 мм2. Он изготавливался по техпроцессу 0.35 мкм и упаковывался в керамический LGA корпус на 599 контактов.[6]

Производные процессоры

R10000 был расширен в нескольких производных проектах. Все производные после R12000 имели сниженные тактовые частоты для сохранения рассеиваемой мощности в пределах от 15 до 20 Вт. Это позволяла плотно упаковывать процессоры в высокопроизводительных вычислительных системах SGI.

R12000

R12000 является производной от R10000, начатой в MIPS и завершенной в SGI. Он изготавливался NEC и Toshiba. Версия от NEC называется VR12000. Микропроцессор был представлен в ноябре 1998 года, он был доступен с частотами 270, 300 и 360 МГц. R12000 был разработан как временное решение после отмены проекта Beast, в котором планировалось создать преемника для R10000. Процессор R12000 использовался NEC, Siemens-Nixdorf, SGI и Tandem Computers (позже стала частью Compaq).

В R12000 улучшена микроархитектура R10000 путем включения дополнительных стадий конвейера для повышения тактовой частоты, увеличения количества записей в таблицах истории ветвлений, улучшения прогнозирования ветвлений, изменения очередей инструкций для учёта возраста инструкций (более старым инструкциям придается приоритет для исполнения).

R12000 изготавливался компаниями NEC и Toshiba по 0.25 мкм КМОП-процессу с четырьмя уровнями алюминиевых соединений. Использование нового техпроцесса не означает, что R12000 был просто усадкой предыдущего дизайна с оптимизациями микроархитектуры. Топология R12000 была оптимизирована для получения преимуществ от 0.25 мкм техпроцесса.[7][8] Изготовленные NEC процессоры VR12000 содержат 7,15 млн транзисторов в кристалле размером 15.7 на 14.6 мм (229.22 мм2).

R12000A

R12000A — производная от R12000, разработанная в SGI. Представлен в июле 2000 года, работает на 400 МГц и изготовлен компанией NEC на 0.18 мкм техпроцессе с алюминиевыми соединениями.

R14000

R14000 является дальнейшим развитием R12000, анонсированным в июле 2001 года. R14000 работает на частоте 500 МГц благодаря применению 0.13 мкм КМОП техпроцесса с пятью уровнями медных межсоединений. Кроме улучшений в микроархитектуре R12000 процессор поддерживает SSRAM с интерфейсом удвоенной скорости передачи данных (DDR) для вторичной кэш-памяти и системную шину с частотой 200 МГц.[9]

R14000A

R14000A является дальнейшим развитием R14000, о котором было объявлено в феврале 2002 года. Он работает на 600 МГц, рассеивает около 17 Вт, и изготовлен компанией NEC по 0.13 мкм КМОП техпроцессу с семью уровнями медных соединений.

R16000

R16000 (кодовое название «N0») — последняя производная R10000. Процессор разработан компанией SGI и изготовлен NEC по нормам 0.11 мкм техпроцесса с восемью уровнями медных межсоединений. Микропроцессор был представлен 9 января 2003 года, дебютировав на частоте 700 МГц для компьютера SGI Fuel. Также использовался в SGI Onyx4 Ultimate Vision.[10] В апреле 2003 года была представлена 600 МГц версия для SGI Origin 350. В R16000 были увеличены до 64 КБ размеры кэша инструкций и данных.

R16000A

Под R16000A обозначают варианты процессоров R16000 с тактовыми частотами выше 700 МГц. Первый R16000A с 800 МГц был представлен 4 февраля 2004 года. Позже появилась 900 МГц версия. Для некоторых клиентов SGI поставлял R16000 с частотой 1.0 ГГц. Среди пользователей R16000 — НР и SGI. SGI использовала микропроцессор в своих Fuel и Tezro рабочих станциях и в серверах Origin 3000. Компания HP использует R16000A в серии отказоустойчивых серверов NonStop Himalaya S-Series (унаследованы от компании Tandem через Compaq).

R18000

R18000 — отмененный проект дальнейшего развития R10000. Запланированные изменения микроархитектуры были представлены Silicon Graphics на симпозиуме Hot Chips в 2001 году. R18000 был разработан специально для SGI ccNUMA серверов и суперкомпьютеров. Каждый узел использовал бы два R18000, подключенных через мультиплексированную шину к системному контроллеру. Он подключает микропроцессоры к локальной памяти и остальной частью системы через сеть топологии гиперкуб.

В R18000 улучшены очереди инструкций с плавающей запятой, а в блоке плавающих операций используется два устройства умножения-сложения, что в 4 раза увеличивает пиковый темп FLOPS. Деление и операция квадратного корня могут выполняться в отдельных неконвейерных устройствах одновременно со сложением и умножением. Значительно переработаны системный интерфейс и иерархия памяти. Используются 52-разрядные виртуальные адреса и 48-битные физические адреса. Двунаправленная мультиплексированная системная шина более ранних моделей заменяется на два однонаправленных DDR канала: 64-разрядную мультиплексированный канал для адресов и записи данных и 128-битный канал чтений. Эти два канала могут разделятся со вторым процессором R18000 посредством мультиплексирования. Шина также может быть переконфигурирована в режимы SysAD или Avalance для обратной совместимости с системами R10000.

R18000 использует 1 МБ четырёх-канальный множественно-ассоциативный кэш второго уровня, реализованный на том же кристалле. Опционально может использоваться кэш третьего уровня, построенный из памяти SDR или DDR SSRAM, либо из или DDR SDRAM с ёмкостью от 2 до 64 МБ. Такой L3 кэш дополнен кэшем тегов в размере 400 КБ, расположенном на кристалле процессора для уменьшения задержек. Для доступа к L3 кэшу используется шина шириной 144-разрядов: 128 бит для данных и 16 бит для ЕСС. Частоты L3 кэша могут настраиваться.

R18000 планировался к изготовлению по NEC техпроцессу «UX5» по нормам 0.13 мкм КМОП с девятью уровнями медных соединений. Этот процесс использует питание 1.2 V, что позволило бы снизить тепловыделение и повысить плотность упаковки в больших системах.

Примечания

- «MIPS Claims Floating-Point Record With R10000, The Hottest Chip At The Microprocessor Forum» (недоступная ссылка) (31 October 1994). Computer Business Review.

- Gwennap, Linley (27 January 1997). «Alpha Sails, PowerPC Flails». Microprocessor Report, pp. 1, 6-9., p. 8."

- «Defects Revealed In SGI R10000 MIPS Systems, Revenues Hit». (26 September 1996). Computer Business Review.

- «SGI To Recall 10,000 R10000s»(30 September 1996). Computer Business Review.

- Yeager, Kenneth C. «The MIPS R10000 Superscalar Microprocessor». IEEE Micro. April 1996, p. 28. doi:10.1109/40.491460

- Gwennap, Linley (24 October 1994). «MIPS R10000 Uses Decoupled Architecture». Microprocessor Report, Volume 8, Number 14., p. 4.

- Gwennap, Linley (6 October 1997). «MIPS R12000 to Hit 300 MHz». Microprocessor Report, Volume 11, Number 13.

- Halfhill, Tom R. (January 1998). «RISC Fights Back with the Mips R12000». Byte Magazine.

- ComputerWire (2 July 2002). «SGI to develop MIPS chips for Origin, Onyx». The Register.

- Silicon Graphics, Inc. (9 January 2003). SGI Boosts Price/Performance on Silicon Graphics Fuel Visual Workstation Family up to 25 %. (Press release).

Ссылки

- ComputerWire (2 July 2002). «SGI to develop MIPS chips for Origin, Onyx». The Register.

- Fu, Tim et al. (31 August 2001). «R18000: The Latest SGI Superscalar Microprocessor». Hot Chips XIII.

- Gwennap, Linley (24 October 1994). «MIPS R10000 Uses Decoupled Architecture». Microprocessor Report, Volume 8, Number 14.

- Gwennap, Linley (27 January 1997). «Alpha Sails, PowerPC Flails». Microprocessor Report, pp. 1, 6-9.

- Gwennap, Linley (6 October 1997). «MIPS R12000 to Hit 300 MHz». Microprocessor Report, Volume 11, Number 13.

- Halfhill, Tom R. (November 1994). «T5: Brute Force». Byte Magazine.

- Halfhill, Tom R. (January 1998). «RISC Fights Back with the Mips R12000». Byte Magazine.

- Heinrich, Joe (29 January 1997). «MIPS R10000 Microprocessor User’s Manual».

- Kanellos, Michael; Kawamoto, Dawn (9 April 1998). «Silicon Graphics scraps MIPS plans». CNET News.

- MIPS Technologies, Incorporated. (October 1994). «R10000 Microprocessor Product Review» (недоступная ссылка).

- Morgan, Timothy Prickett (16 April 2003). «SGI Announces Origin 350 Midrange HPC Server». IT Jungle.

- NEC Corporation (24 November 1998). NEC Markets World’s Highest Class Performance Microprocessor. (Press release).

- Shankland, Stephen (15 April 2003). «SGI updates midrange Unix server». CNet News.

- Silicon Graphics, Inc. (9 January 2003). SGI Boosts Price/Performance on Silicon Graphics Fuel Visual Workstation Family up to 25 %. (Press release).

- Vasseghi, N. et al. (November 1996). «200-MHz superscalar RISC microprocessor». IEEE Journal of Solid-State Circuits 31 (11): pp. 1675—1686.

- Yeager, Kenneth C. (April 1996). «The MIPS R10000 Superscalar Microprocessor» (недоступная ссылка). IEEE Micro.

- Yeager, Kenneth C. (August 1995). «R10000 Superscalar Microprocessor». Hot Chips VII.

- В. Аваков, Микропроцессор MIPS R10000 — Открытые системы. СУБД 1995 № 06

- Андрей Борзенко, Микропроцессоры MIPS, Виртуальный компьютерный музей; журнал «PC Week» (294)24' 2001

- R10000 в Linux MIPS wiki (англ.)

- Олег Коленченко, Эволюция процессоров. Часть 4: архитектура RISC и развитие индустрии в 1990-е годы, ferra.ru, 25 июля 2014

- Глава 15. Серверы компании Silicon Graphics / В.З. Шнитман, С.Д. Кузнецов, Серверы корпоративных баз данных. Материалы Центра Информационных Технологий (не позднее 1999 года)