Планарная технология

Планарная технология — совокупность технологических операций, используемых при изготовлении планарных (плоских, поверхностных) полупроводниковых приборов и интегральных микросхем. Процесс включает в себя формирование отдельных компонентов транзисторов, а также объединение их в единую структуру. Это основной процесс при создании современных интегральных схем. Данная технология была разработана Жаном Эрни, одним из членов «вероломной восьмёрки», во время работы в Fairchild Semiconductor. Технология впервые была запатентована в 1959 году.

Сутью концепции было рассмотрение схемы в проекции на плоскости, что позволяло использовать элементы фотографии, такие как негативные фотоплёнки при засвечивании светочувствительных реактивов. Последовательность таких фотопроекций позволила создавать на кремниевой подложке сочетания диоксида кремния (диэлектрик) и легированных участков (проводники). Применяя также металлизацию (для соединения элементов схемы) и концепцию изоляции элементов схемы p-n-переходами, предложенную Куртом Леговцом, исследователи в Fairchild смогли создать схему на одной кремниевой пластине («вафля»), изготовленной из монокристалического кремниевого слитка («буля»).

Процесс также включает в себя операции окисления кремния (SiO2), травления и диффузии.

Принципы технологии

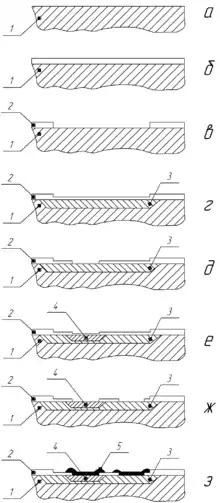

а — исходная пластина; б — первое окисление; в — первая фотолитографическая обработка; г — создание базовой области и второе окисление; д — вторая фотолитографическая обработка; е — создание эмиттерной области и третье окисление; ж — третья фотолитографическая обработка; з — металлизация.

1 — полупроводник с электропроводностью n-типа; 2 — маскирующая плёнка диоксида кремния; 3 — область базы; 4 — область эмиттера; 5 — металлическая плёнка (электроды).

На вход технологии поступают пластины, называемые подложками. Состав материала подложек, кристаллическая структура (вплоть до межатомных расстояний в подложках для современных процессоров) и кристаллографическая ориентация строго контролируются. В ходе технологического процесса в приповерхностном слое полупроводникового материала, являющегося подложкой или нанесённого на подложку, создают области с различным типом или величиной проводимости, определяемой в конечном счёте различной концентрацией донорных и акцепторных примесей, а также материалом слоя. Поверх слоя полупроводникового материала, с использованием в нужных местах прослоек диэлектрического материала, наносятся слои проводящего материала, образующего контактные площадки и необходимые соединения между областями. Области и слои проводника, полупроводника и диэлектрика в совокупности образуют структуру полупроводникового прибора или интегральной микросхемы.

Особенность планарной технологии состоит в том, что после завершения каждой технологической операции восстанавливается плоская (планарная) форма поверхности пластины, что позволяет создавать достаточно сложную структуру, используя конечный набор технологических операций.

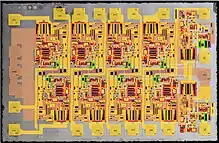

Планарная технология обеспечивает возможность одновременного изготовления в едином технологическом процессе огромного числа дискретных полупроводниковых приборов или интегральных микросхем на одной подложке, что позволяет существенно снизить их стоимость. Также в случае изготовления на одной пластине идентичных приборов параметры всех приборов оказываются близкими. Ограничителем является только площадь подложки, поэтому диаметр подложек по мере развития технологий производства подложек стремятся увеличивать.

Для контроля качества выполнения промежуточных операций на подложке, как правило, выделяют несколько малых областей (обычно в центре и на периферии), на которых в ходе штатного технологического процесса формируются тестовые проводящие дорожки и элементарные приборы (конденсаторы, диоды, транзисторы и т. п.). В этих же областях формируют контактные площадки относительно большой площади для тестирования годности пластин перед скрайбированием (разделением на отдельные приборы). Для совмещения изображений при фотолитографии также в специально выделенной области формируются знаки совмещения, подобные тем, какие можно встретить на многоцветной печатной продукции.

Основные технологические операции

Литография

Основные технологические операции, используемые в планарной технологии, основаны на процессе литографии (фотолитографии).

Применяются следующие способы:

- оптическая фотолитография (стандартная), λ=310—450 нм;

- ультрафиолетовая фотолитография на эксимерных лазерах, λ=248 нм, λ=193 нм;

- фотолитография в глубоком ультрафиолете, λ=10—100 нм;

- рентгеновская литография, λ=0,1—10 нм;

- электронная литография;

- ионно-лучевая литография;

- нанопечатная литография.

Приёмы применяемой фотолитографии могут быть сканирующими и проекционными; контактными, бесконтактными и на микрозазоре (см. также иммерсионная литография). Также может быть ограниченно применён способ радиационно-стимулированной диффузии.

- Литографическое оборудование

EUV-литографические машины голландской компании ASML лежат в основе современного производства микросхем.

Цепочка операций

Технологическая цепочка состоит из серии циклов (до нескольких десятков), включающих в себя следующие основные операции (в порядке следования):

- подготовка подложки: применяется механическая и химическая полировка для получения плоской поверхности без механических дефектов (выполняется 1 раз при поступлении подложки в техпроцесс);

- формирование на поверхности подложки слоя необходимого материала с заданной структурой: эпитаксиальное наращивание, осаждение диэлектрических или металлических плёнок (операция выполняется не в каждом цикле);

- создание на поверхности подложки защитного слоя: в случае кремниевых подложек для этого используется окисление поверхности, для удешевления процесса, а также в случае других подложек часто используется осаждение (CVD-процесс) слоя диоксида или нитрида кремния, либо другого материала с низким коэффициентом диффузии легирующих примесей. Толщина слоя подбирается так, чтобы за время, необходимое для создания легированной области необходимой конфигурации в подложке, легирующий элемент не достиг подложки сквозь защитный слой;

- нанесение слоя фоторезиста, обладающего устойчивостью к используемым травителям;

- совмещение изображений по знакам совмещения и экспонирование рисунка окон на слой фоторезиста (выполняется на степперах);

- удаление (проявление) исключительно засвеченных (либо незасвеченных — зависит от типа фоторезиста) участков слоя фоторезиста;

- стравливание защитного слоя с подложки на участках, не закрытых фоторезистом;

- удаление остатков слоя фоторезиста;

- возможная операция: внедрение легирующих примесей нередко проводят в двухстадийном процессе, разделяя фазы загонки примеси в приповерхностную область и разгонки загнанной примеси по требуемому объёму (отжига); загонка производится путём локальной (с поверхности или из газовой фазы) диффузии или ионной имплантации легирующих примесей через окна в защитном слое в поверхность подложки; режимы диффузии (имплантации) подбираются так, чтобы за время этой и всех последующих технологических операций размер легированной области достиг требуемых размеров по площади и глубине, а нарушенная радиацией при ионном легировании кристаллическая решётка восстановилась;

- возможная операция: плазменное или химическое травление поверхности подложки для удаления излишков слоя ранее осаждённого материала.

- плазменное или химическое травление поверхности подложки для удаления защитного слоя (выполняется не в каждом цикле).

- планаризация[2] (сглаживание неровностей) поверхности перед переходом к новому циклу, например при помощи процесса CMP.

Основные циклы, выполняемые при создании полупроводниковых приборов, следующие:

- формирование областей р-типа (локальное внедрение примесей)

- формирование областей n-типа (локальное внедрение примесей)

- формирование проводящих дорожек и контактных площадок (удаление излишков слоя металла). См. также омический контакт.

Схемы чередования операций и циклов бывают достаточно сложны, а их количество может измеряться десятками. Так, например, при создании микросхем на биполярных транзисторах с коллекторной изоляцией, с комбинированной изоляцией (изопланар-1,2; полипланар) и в других схемах, где необходимо или желательно обеспечить снижение сопротивления коллектора и повышение быстродействия), сначала выполняется оксидирование, фотолитография и диффузия под захоронённый n+ слой, затем наращивается эпитаксиальный слой полупроводника («захоранивание») и уже в эпитаксиальном слое создаются конкретные элементы микросхемы. После этого поверхность пластины снова изолируют, выполняют контактные окна и наносят проводящие дорожки и контактные площадки. В сложных микросхемах контактные дорожки могут выполняться в несколько уровней с нанесением между уровнями диэлектрических прослоек, опять же с вытравленными окнами.

Порядок циклов в первую очередь определяется зависимостями коэффициентов диффузии примесей от температуры. Стараются сначала производить загонку и разгонку примесей менее подвижных, и для сокращения времени процесса использовать более высокие температуры. Затем при меньших температурах загоняют и разгоняют более подвижные примеси. Это связано с быстрым (экспоненциальным) падением коэффициента диффузии при понижении температуры. К примеру, в кремнии сначала при температуре до ~950 °C создают области р-типа, легированные бором, и только потом при температуре менее ~750 °C создают области n-типа, легированные фосфором. В случае других легирующих элементов и/или других матриц номиналы температур и порядок создания легированных областей может быть разным, но всегда при этом стараются придерживаться правила «понижения градуса». Создание дорожек всегда выполняется в завершающих циклах.

Помимо диффузионного легирования и разгонки могут применяться методы радиационной трансмутации кремния в алюминий и фосфор. При этом проникающая радиация помимо запуска реакций трансмутаций заметно повреждает кристаллическую решётку подложки. Легирование пластины идёт по всей площади и по всему объёму материала, распределение образующихся примесей определяется интенсивностью проникающего в толщу вещества излучения и поэтому подчиняется закону Бугера-Ламберта:

- N=N0*e-ax, где

- N — концентрация примеси;

N0 — концентрация примеси на поверхности; a — коэффициент поглощения излучения; x — расстояние от облучаемой поверхности;

Для легирования обычно использовали слитки кремния, не разрезанные на пластины. В этом случае профиль распределения примеси по диаметру пластины описывается транспозицией экспонент с максимумом на периферии пластины и минимумов в центре пластины. Этот метод имеет ограниченное применение для изготовления специальных приборов из высокоомного кремния.

Завершающие операции при производстве микросхем

Скрайбирование

По завершении операций по формированию приборов на пластине производится разделение пластины на малые кристаллы, содержащие единственный готовый прибор.

Изначально разделение пластины на отдельные кристаллы велось путём процарапывания её на глубину 2/3 от толщины пластины алмазным резцом с последующим раскалыванием по процарапанной линии. Этот принцип разделения дал название всей операции разделения пластин на кристаллы: «скрайбирование» (от англ. scribe — "размечать").

В настоящее время скрайбирование может выполняться как с прорезанием на полную толщину пластины с образованием отдельных кристаллов, так и на часть толщины пластины с последующим раскалыванием на кристаллы.

Скрайбирование с некоторой натяжкой можно отнести к завершающим этапам планарной технологии.

Прорезание может выполняться различными путями:

- Скрайбирование алмазным резцом — процарапывание пластины вдоль одной из кристаллографических осей для последующего разламывания по рискам подобно тому, как действуют при резке стекла. Так, на кремниевых подложках разломы лучше всего получаются по плоскостям спайности. В настоящее время метод является устаревшим и практически не используется;

- Раскалывание локальным термоударом (применяется мало);

- Резка кольцевой пилой с внешней режущей кромкой: установка похожа на установку для резки слитка на пластины, но диаметр диска значительно меньше и режущая кромка выступает за зажимы не более, чем на полторы глубины риски. Это сводит к минимуму биения и позволяет увеличить частоту вращения до 20-50 тыс. оборотов в минуту. Иногда на ось надевают несколько дисков для одновременного создания нескольких рисок. Способ позволяет прорезать пластину на всю толщину, но обычно используется для процарапывания с последующим раскалыванием.

- Химическое скрайбирование — это скрайбирование путём сквозного химического травления. Для проведения операции предварительно делается фотолитография с формированием окон на разделительных участках с обеих сторон пластины и вытравливаются разделительные области. Разновидностью данного метода является сквозное анизотропное травление, где используется разница в скорости травления в различных направлениях кристаллографических осей. Основные недостатки ограничивающие применение метода — сложность совмещения рисунка окон для травления обеих сторон пластины и боковое вытравливание кристаллов под маской. Способ позволяет как протравить пластину на часть толщины, так и на всю толщину.

- Резка стальными полотнами или проволоками — полотна или проволока трутся о пластины, на место соприкосновения подается абразивная суспензия. Существует риск порчи готовых структур лопнувшим полотном или проволокой. Колебания состава суспензии, механические перекосы в оборудовании также могут приводить к появлению брака. Метод использовался в мелкосерийных производствах и лабораториях. Способ позволяет прорезать пластину всю толщину, но обычно используется для процарапывания с последующим раскалыванием.

- Резка лазерным лучом: образование рисок происходит в результате испарения материала подложки сфокусированным лазерным лучом. Применение метода ограничивается толщиной пластин, а так как больший диаметр пластин требует большей толщины для сохранения требуемой жёсткости, не всегда используется сквозное разделение (менее 100 мкм — возможно резание, от 100 до 450 мкм — только скрайбирование). При сквозном разделении не требуется последующей ломки пластины на кристаллы. Не рекомендуется использовать данный метод для резки пластин, содержащих арсенид галлия, из-за выделения высокотоксичных соединений. В СССР для этого метода в основном использовались лазеры из алюмо-иттриевого граната и рубина. Основной проблемой при использовании резки лазерным лучом является защита готовых структур от капель расплавленного и конденсации на них испарённого материала подложки. Оригинальным способом решения этой проблемы является использование при лазерной резке в качестве фокусирующего световода и одновременно хладагента тонкого шнура воды, подаваемой под высоким давлением.

После прорезания рисок пластины разделяют на кристаллы. Существует три основных метода:

- Метод подпружиненного ролика: пластину укладывают в полиэтиленовый пакет и размещают на толстом упругом резиновом основании рисками вниз и оператор прокатывает вдоль рисок подпружиненным роликом. Качество разламывания зависит от того, насколько направление движения ролика параллельно рискам, при отклонении возможно раскалывание не по рискам и порча кристаллов.

- Разламывание на полусфере: пластины обжимаются эластичной мембраной по сферической поверхности. На мембрану давят либо гидравлическим способом, либо сжатым воздухом. При разделении этим способом пластин диаметром более 76 мм резко увеличивается процент брака.

- Прокатка между двумя цилиндрическими валиками. Пластину на липкой ленте-носителе сжимают стальным и резиновым валиком, которые вращаются, в результате деформации упругого резинового валика к пластине прикладывается изгибающее усилие.

Крепление кристаллов к корпусу

После скрайбирования кристаллы присоединяют к основанию корпуса:

- методом приклеивания — используются клеи на основе эпоксидной смолы, со временем деградирует: хуже проводит тепло, становится хрупкой, соединение становится непрочным. Данный метод в настоящее время не используется.

- метод эвтектического сплавления: на керамическое основание корпуса и на обратную сторону пластины перед разделением на кристаллы наносится тонкий слой золота. В месте крепления кристалла помещается золотая фольга, кристалл кладут на основание корпуса, подогревают до 380° (температура эвтектики системы кремний - золото 385°) и прикладывают вертикальное усилие. Высокая стоимость позволяет использовать метод только для схем спецназначения.

- при герметизации пластмассой кристаллы с приваренной арматурой размещают на ленте-носителе.

- соединение стёклами — ввиду сложности подбора стекла с низкой температурой размягчения и температурным коэффициентом линейного расширения, соответствующим используемым материалам, данный метод для тонкоплёночной технологии малопригоден (годится для гибридныx и толстоплёночных интегральных схем)

- метод «перевёрнутого кристалла» — при использовании объёмных выводов одновременно подсоединяются и кристалл и все выводы.

Присоединение выводов к кристаллу

методы присоединения выводов:

- термокомпрессионная сварка

- ультразвуковая сварка

- косвенного импульсного нагрева

- сварка сдвоенным электродом

- лазерная точечная сварка

- электронно-лучевая сварка

- беспроволочный монтаж элементов с объёмными выводами

Герметизация кристалла

методы герметизации — выбор метода зависит от материала и формы корпуса. Корпуса бывают герметичные (металло-стеклянные, металло-керамические, керамические, стеклянные) и негерметичные (пластмассовые, керамические). Сварка: холодная сварка; электроконтактная сварка: контурная, роликовая, микроплазменная, аргонно-дуговая, лазерная, электронно лучевая; Пайка: конвективная в печах, струёй горячего газа; склеивание; герметизация пластмассой.

Тестирование

При тестировании контролируется качество крепления выводов, а также устойчивость приборов (кроме негерметичных) к экстремальным климатическим условиям на стенде тепла и влаги и механическим воздействиям на ударном и вибростенде, а также их электрические свойства. После тестирования приборы окрашивают и маркируют.

Примечания

- Hoerni, J. A. Патент US3025589 Method of Manufacturing Semiconductor Devices. — 1959.

- «Цифровые интегральные схемы. Методология проектирования.»="Digital Integrated Circuits" 2-е изд, 2007 ISBN 978-5-8459-1116-2 стр 75

Литература по теме

- Черняев В. Н., «Технология производства интегральных микросхем и микропроцессоров», М.: Радио и связь, 1987.

- И. А. Малышева «технология производства интегральных микросхем» издательство «Радио и связь» 1991

- Моряков О. С. «Устройство и наладка оборудования полупроводникового производства» издательство «высшая школа» 1976.

- Ю. В. Панфилов В. Т. Рябов Ю. Б. Цветков «Оборудование производства интегральных микросхем и промышленные роботы» издательство «Радио и связь» 1988.

- В. В. Пасынков Л. К. Чиркин А. Д. Шинков «Полупроводниковые приборы» издательство «Высшая школа» 1973.

- «Конструирование и технология микросхем» под ред. Л. А. Коледова издательство «Высшая школа» 1984.

- И. М. Николаев Н. А. Филинюк «Интегральные микросхемы и основы их проектирования» издательство «Радио и связь» 1992