Код Джонсона

Код Джо́нсона — разновидность двоичной системы счисления, в которой два соседних кода различаются только в одном двоичном разряде.

История

В 1953 году Роберт Ройс Джонсон разработал ряд различных счетчиков на основе регистра сдвига с разным количеством состояний с простой логической схемой в цепи обратной связи и подал заявку на патент[1]. Счетчик, работающий в коде Джонсона, является самым простым из них.

Принципы формирования кода Джонсона

| N | Биты | |||

|---|---|---|---|---|

| 4 | 3 | 2 | 1 | |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 1 | 1 |

| 4 | 1 | 1 | 1 | 1 |

| 5 | 1 | 1 | 1 | 0 |

| 6 | 1 | 1 | 0 | 0 |

| 7 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

- Формирование кода Джонсона осуществляется сдвигом со стороны правых в сторону левых разрядов, причём вдвигаемый очередной бит разряда равен логической 1 до тех пор, пока во всех разрядах не будут логические единицы. После этого в том же порядке (со стороны правых в сторону левых разрядов) сдвигаются логические нули до тех пор, пока во всех разрядах не останутся только логические нули.

- Код Джонсона — код с избытком, то есть для числа разрядов больше 2 в коде Джонсона для кодирования некоторого числа состояний требуется большее число разрядов, чем в позиционном двоичном коде]].

- Код Джонсона — помехозащищённый код. Это означает, что каждая последующая комбинация отличается от предыдущей значением только одного разряда, или расстояние Хэмминга между соседними кодовыми комбинациями равно 1.

- В схемотехнике счётчиков это свойство устраняет одновременное переключение многих элементов, характерное для двоичных счётчиков при некоторых переходах. Одновременное переключение многих триггеров создает токовые импульсы с большой амплитудой в цепях питания схем, которые могут вызвать сбои в работе логической схемы.

- Код Джонсона — циклический код. То есть, последняя комбинация отличается от первой также значением только одного разряда.

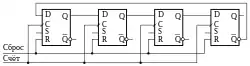

Счётчик в коде Джонсона

На рисунке приведена схема двоичного 4-х битового счетчика, работающего в коде Джонсона. Изменения состояния битов этого счётчика соответствуют приведённым в таблице. После подачи импульса на линию «Сброс» все разряды счётчика устанавливаются в состояние логического 0, при этом на D-входе первого D-триггера будет присутствовать логическая 1, так как на этот вход подаётся сигнал с инверсного выхода четвёртого триггера. По нарастающему фронту тактирующего импульса «Счёт» первый триггер установится в состояние логической 1 которая передаётся на D-вход второго триггера. Очередной тактовый импульс переведёт этот триггер в состояние логической 1 и т. д. После подачи 4 тактовых импульсов все триггеры перейдут в состояние логической 1, и на входе 1-го триггера установится логический 0, далее триггеры последовательно будут принимать состояние логического 0, пока все триггеры не установятся в состояние логического нуля, — исходного начального состояния.

Примечания

- Robert Royce Johnson, «Electronic counter», US Patent No. 3030581, filed in 1953.